# Sub-Nanosecond Pulses Enable Partial Reset for Analog Phase Change Memory

Keren Stern, Nicolás Wainstein<sup>®</sup>, *Member, IEEE*, Yair Keller, Christopher M. Neumann<sup>®</sup>, Eric Pop<sup>®</sup>, *Senior Member, IEEE*, Shahar Kvatinsky, *Senior Member, IEEE*, and Eilam Yalon<sup>®</sup>, *Member, IEEE*

Abstract—A key bottleneck in using phase change memory (PCM) for training artificial neural networks is the abrupt nature of the melt-quench process (amorphization), which does not allow gradual reset. Here we demonstrate analog reset (partial amorphization) in PCM by applying sub-nanosecond programming pulses. Intermediate-level reset states are enabled by reducing the pulse width below the dominant thermal time constant of the PCM, which is on the order of a few nanoseconds. We show gradual change in PCM resistance as a function of number of (sub-ns) reset pulses with 50 intermediate states. Our unique scheme allows fine-tuning the resistance with sub-ns pulses of constant amplitude, which can significantly reduce the programming complexity in training neuromorphic hardware.

**Index Terms**—Analog PCM, partial reset, sub-ns pulses, multi-level PCM, neuromorphic devices, resistance drift.

#### I. INTRODUCTION

PHASE change memory (PCM) has matured as a storage class memory, and is more recently being evaluated for neuromorphic hardware [1]–[3]. PCM relies on the large resistivity contrast between the crystalline (low resistive state, LRS) and amorphous (high resistive state, HRS) phases in chalcogenide compounds, such as Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST). The phase transition is induced thermally using electrical pulses of crystallization (set) and amorphization (reset) [2].

In neuromorphic applications, synapses are important building blocks. With their adjustable conductance, PCM devices can store (and train) weights of the neural network, and efficiently implement the vector-matrix multiplication required for artificial neural networks [1], [4]–[6]. This requires analog-type behavior *i.e.*, a gradual change in resistance. However, the amorphization in PCM is based on a melt-quench

Manuscript received June 11, 2021; revised June 30, 2021; accepted July 1, 2021. Date of publication July 5, 2021; date of current version August 26, 2021. This work was supported in part by the Israel science foundation (ISF) Grant 1179/20, in part by the Russel Berrie Nanotechnology Institute (RBNI) Seeding Grant (NEVET), and in part by the Member Companies of the Stanford Nonvolatile Memory Technology Research Initiative (NMTRI). The review of this letter was arranged by Editor H. Wu. (Corresponding author: Eilam Yalon.)

Keren Stern, Nicolás Wainstein, Yair Keller, Shahar Kvatinsky, and Eilam Yalon are with the Viterbi Faculty of Electrical and Computer Engineering, Technion–Israel Institute of Technology, Haifa 32000, Israel (e-mail: eilamy@technion.ac.il).

Christopher M. Neumann and Eric Pop are with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2021.3094765.

Digital Object Identifier 10.1109/LED.2021.3094765

process which typically results in abrupt reset, *i.e.* a sharp resistance change. Previous studies therefore tuned PCM resistance by partial crystallization (set only) [7]–[12], by applying reset pulses with varying amplitude [9], [13], [14], or by using special structures and initialization steps [15], which significantly increases programming complexity.

In this work, we show that partial amorphization (analog reset of PCM), which allows for bi-directional weight update, can be achieved with constant amplitude, sub-nanosecond (ns) pulses, without initialization or dedicated cell structures. Analog reset behavior is enabled using pulse widths (PWs) shorter than the dominant thermal time constant of the device  $(\tau_{th})$ . We also carry out dynamic measurements of the transient resistance and show that  $\tau_{th}$  is in the range of  $\sim$ 1-3 ns in our confined PCM devices with diameter  $\sim$ 100-200 nm. Our technique can be used in any PCM cell structure, and we envision that this approach can advance the implementation of PCM technology for future neuromorphic applications.

# II. HIGH-SPEED MEASUREMENT SETUP AND CONFINED-CELL PCM DEVICES

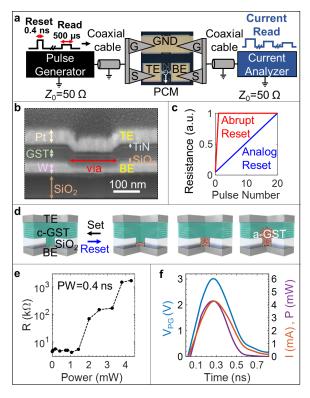

We used conventional PCM cells of confined GST, fabricated as outlined below, and we utilized a high-speed measurement setup, including transmission lines for the access pads, to carry out sub-ns programming. The high-speed measurement setup (Fig. 1a) consists of a fast pulse generator (PG) connected in series with the PCM device and a current analyzer. Ground-signal (GS) transmission lines matched to 50  $\Omega$  are used to connect the device with the measurement equipment. The output impedance of the PG, as well as the input impedance of the current analyzer are also set to 50  $\Omega$ .

The focused ion beam (FIB) scanning electron microscope (SEM) cross-section of a confined PCM cell is shown in Fig. 1b, fabricated as follows [16]. First, tungsten (W) was evaporated, patterned, and etched to form the bottom electrode (BE). Next, SiO<sub>x</sub> was deposited using plasma enhanced chemical vapor deposition (PECVD) and the confined vias were patterned using electron-beam lithography. The BE was Ar sputter-cleaned to remove oxidation and prevent filament formation, followed by GST and TiN sputter deposition, all without breaking vacuum. The TE is completed with additional TiN/Pt, and along with the contact pads it is patterned by lift-off.

The devices are initially set to their LRS, and partial reset (Fig. 1c) is achieved by applying short pulses. The resistance

0741-3106 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. (a) High speed setup and schematic of the sequential program and read pulses, including transmission lines and ground-signal (GS) probes for minimizing parasitic capacitance effects. (b) Cross section FIB-SEM of the confined GST PCM device. GST is confined in a via-hole (marked by the red arrow) in SiO $_2$  with varying diameter in the range 100-200 nm. (c) Schematic illustration of typical PCM abrupt reset (red) vs. the analog gradual reset desired for neuromorphic devices (blue). Schematic of the sequential program and read pulses. (d) Illustration of a gradual formation of amorphous volume for sub-ns reset. The concept is demonstrated here for confined cells, but it is also valid for mushroom cells and other PCM device structures. (e) Resistance vs. applied reset power at 0.4 ns PW. Before each reset pulse the PCM was set to an initial state of  $\sim$ 1-3 kΩ. (f) Transient waveform of a 0.4 ns reset pulse: applied voltage (blue), measured current (orange) and power (purple).

state is read at low voltage (0.1 V) after each pulse as shown schematically in Fig. 1a. This way, gradual reset, as opposed to abrupt switching, is achieved (see Fig. 1c). The gradual change in the volume of the amorphous phase is schematically illustrated in Fig. 1d. The full range of resistance obtained in our devices is shown in Fig. 1e, and the transient waveform of a 0.4 ns reset pulse is displayed in Fig. 1f.

# III. RESULTS AND DISCUSSION

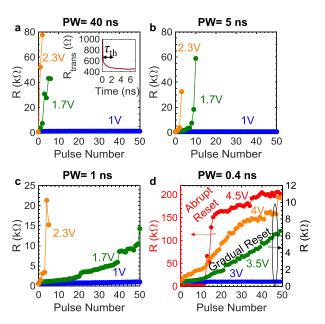

Our partial amorphization scheme is enabled by pulses shorter than the dominant thermal time constant of the device  $(\tau_{th})$ . We characterized this  $\tau_{th}$  experimentally by dynamic measurements of the transient resistance and found that it is in the range of  $\sim$ 1-3 ns for our devices (Fig. 2a inset). This  $\tau_{th}$  corresponds to the time it takes a critical volume of GST to reach the melting temperature [17]. It can be evaluated for a given material, device structure, and GST volume by the product of the thermal resistance and heat capacitance in a simplified lumped model  $R_{th}$   $C_{th}$ ; the specific heat capacity of GST is  $c_{GST} \sim 1.3$  J/cm<sup>3</sup>/K [18], and  $R_{th}$  could be dominated by interfaces (thermal boundary resistance, TBR $\sim$ 30 m<sup>2</sup>K/GW [19]). Here the GST thickness is  $\sim$ 50 nm

Fig. 2. Gradual reset with sub-ns pulses shown by read resistance vs. pulse number for varying reset pulse width: (a) 40 ns, (b) 5 ns, (c) 1 ns, (d) 0.4 ns. As the PW is reduced below the thermal time constant ( $\tau_{th} \sim 1$ -3 ns, see panel a inset) reset pulses achieve partial amorphization, exhibiting intermediate resistance states and analog reset. Results are shown for device with via diameter of 175 nm. Abrupt reset is shown for comparison in (d) at higher applied voltage (red).

and the via diameter (Fig. 1b) varies between  $\sim 100$  and 200 nm. In the simple expression given here  $\tau_{\rm th} \approx 2$  ns, considering  $R_{\rm th} = {\rm TBR}/A$  and  $C_{\rm th} = c_{\rm GST} \ V$ , where A is the confined area and V is the GST volume.

The key results of our partial reset experiment are summarized in Fig. 2, showing the evolution of the (read) resistance vs. programming pulse number with varying PWs: (a) 40 ns, much longer than  $\tau_{th}$ , (b) 5 ns, marginally longer than  $\tau_{th}$ , (c) 1 ns, comparable to  $\tau_{th}$ , and (d) 0.4 ns, shorter than  $\tau_{th}$ . Evidently, as the PW is reduced below  $\tau_{th}$  more intermediate resistance states are achieved, and the reset becomes more gradual. Overall, Fig. 2d shows  $\sim$ 50 intermediate resistance states in the range of  $\sim$ 0.5 k $\Omega$  to  $\sim$ 9 k $\Omega$  with nearly linear dependence on number of pulses. This is our main finding and it should be emphasized that such intermediate states were obtained to date only by partial crystallization (set) [7]–[12], or by varying reset pulse amplitude [9], [13], [14].

Fig. 2 presents results for devices with via diameter of 175 nm, but devices with nominal via diameter sizes in the range  $\sim$ 100-200 nm were also measured, exhibiting similar behavior. For a given pulse voltage amplitude, the resistance saturates after a certain number of pulses (*e.g.*, see orange markers beyond pulse number 30 in Fig. 2d). We note that the resistance range is lower for shorter PWs, yet it preserves an off/on ratio of nearly  $20\times$  and for neuromorphic applications the requirement for analog behavior can outweigh a larger dynamic range [20], [21]. Pulses shorter than  $\tau_{\rm th}$  may require higher power (*P*), but the energy consumption ( $E \sim P \cdot PW$ ) is not increased because the pulse duration is shorter [22]. Moreover, the alternative method to gradually increase the PCM resistance to an intermediate state (depression) is by first applying a full reset pulse, followed by multiple set

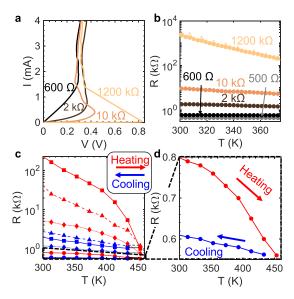

Fig. 3. (a) Current-voltage characteristics of various intermediate resistance states showing the threshold voltage increases with the resistance, corresponding to larger amorphous volume. (b) Temperature-dependent PCM resistance in a limited range below the crystallization temperature for different intermediate states. 500  $\Omega$  is considered fully crystalline and 1200  $\mathrm{k}\Omega$  is considered fully amorphous. Circles represent heating and rectangles represent cooling, which was measured to ensure no phase transition occurred. The amorphous phase has a large negative TCR, fcc has low negative TCR, and hcp has near zero TCR. (c) Non-volatile decrease of resistance upon heating to the (fcc) crystallization temperature ( $\sim$ 450 K) of different intermediate resistance states, indicating phase transition from amorphous to fcc. Each shape represents different initial reset state. Red and blue colors for heating and cooling, respectively. (d) Zoomed in plot of the transition temperature for low resistance state of 0.8 k $\Omega$ . Note the resistance in (c) is in log-scale and in (d) linear scale.

pulses (potentiation). We also point out that we demonstrate the gradual reset with confined PCM cells here, but we expect that gradual amorphization will be more efficient in mushroom cells and bridge devices because they are less limited by interfaces and contacts, and therefore have greater dependence on the volume of the amorphous phase compared with confined cells [15].

To better understand the nature of the obtained multilevel states we perform electrical analysis, including threshold voltage characterization, and resistance *vs.* temperature measurements up to the crystallization temperature. We measured the threshold voltage for different intermediate states because it can represent the change in the amorphous volume due to fixed electric field at the threshold point [23], and because the Ovonic threshold switching phenomenon is a unique signature of amorphous chalcogenide semiconductors [24].

Current vs. voltage (*I-V*) curves for different states are shown in Fig. 3a. The increasing threshold voltage, from ~0.2 to ~0.8 V illustrates the presence of a mixed crystalline-amorphous phase, with increasing amorphous volume corresponding to higher resistance. In addition, the temperature-dependent resistance of intermediates states (Fig. 3b-d) show an increase in the (negative) temperature coefficient of resistance (TCR) at higher resistance states, and a drop in the resistance at the crystallization temperature to the fcc phase (~450 K) indicating presence of partial amorphization rather than mixed fcc-hexagonal phase.

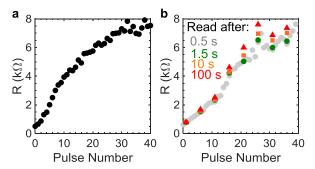

Fig. 4. Resistance drift. (a) Read resistance vs. number of pulses showing partial reset measurement without drift test. (b) Resistance drift effect for partial reset. The resistance is read every 5 pulses after 1.5 s, 10 s and 100 s (green circle, orange square and red triangle, respectively).

Finally, we explore the effect of resistance drift on our subns analog reset scheme. This is an important phenomenon to investigate because it can severely limit the accuracy of conductance tuning, depending on the time scale of the training. In this test, we perform read operations after five programming pulses in time steps of 1.5 s, 10 s, and 100 s (see Fig. 4). Drift becomes more prominent at higher resistance states, as expected, owing to larger volume of amorphous phase [21]–[24].

Interestingly, the drift effect is "erased" by the subsequent reset pulses. This is shown in Fig. 4b, where the resistance state after a drift measurement (color markers in Fig. 4b) continues from the previous non-drifted state (gray) rather than the "drifted state" (red marker). It should also be noted that a critical conduction path in the PCM must melt to achieve re-amorphization, because heating the material to its melting temperature requires high current and low (transient) resistance. We therefore attribute the gradual change in amorphous volume with increasing number of pulses to the dependence of the melted volume on the initial electrical and thermal resistance of the PCM cell. At constant pulse amplitude, the pulse width must be sufficiently short to allow for such fine control of the obtained amorphous volume and the resulting electrical and thermal resistance. Future work should focus on bi-directional weight update (including potentiation) and improving the precision.

## IV. CONCLUSION

We used sub-nanosecond pulse-width programming to demonstrate analog type reset in PCM. This unique behavior, which is essential for neuromorphic applications, is enabled by pulses shorter than the thermal time constant of a critical PCM volume (here  $\sim$ 1-3 ns). The presented method and results can advance the implementation of PCM technology for future neuromorphic applications, and can help enable training with PCM-based artificial intelligence (AI) hardware.

### **ACKNOWLEDGMENT**

Fabrication was performed at the Stanford Nanofabrication Facility (SNF), Stanford Nano Shared Facilities (SNSF), and the Technion Micro-Nano Fabrication & Printing Unit (MNF&PU).

#### REFERENCES

- [1] G. W. Burr, R. M. Shelby, A. Sebastian, S. Kim, S. Kim, S. Sidler, K. Virwani, M. Ishii, P. Narayanan, A. Fumarola, L. L. Sanches, I. Boybat, M. L. Gallo, K. Moon, J. Woo, H. Hwang, and Y. Leblebici, "Neuromorphic computing using non-volatile memory," *Adv. Phys. X*, vol. 2, no. 1, pp. 89–124, Jan. 2017, doi: 10.1080/23746149.2016.1259585.

- [2] S. W. Fong, C. M. Neumann, and H.-S.-P. Wong, "Phase-change memory—Towards a storage-class memory," *IEEE Trans. Electron Devices*, vol. 64, no. 11, pp. 4374–4385, Nov. 2017.

- [3] D. Kuzum, S. Yu, and H.-S. P. Wong, "Synaptic electronics: Materials, devices and applications," *Nanotechnology*, vol. 24, no. 38, Sep. 2013, Art. no. 382001, doi: 10.1088/0957-4484/24/38/382001.

- [4] A. Sebastian, M. Le Gallo, and E. Eleftheriou, "Computational phase-change memory: Beyond von Neumann computing," *J. Phys. D, Appl. Phys.*, vol. 52, no. 44, Aug. 2019, Art. no. 443002, doi: 10.1088/1361-6463/ab37b6.

- [5] S. R. Nandakumar, M. Le Gallo, I. Boybat, B. Rajendran, A. Sebastian, and E. Eleftheriou, "A phase-change memory model for neuromorphic computing," *J. Appl. Phys.*, vol. 124, no. 15, Oct. 2018, Art. no. 152135, doi: 10.1063/1.5042408.

- [6] R. A. Nawrocki, R. M. Voyles, and S. E. Shaheen, "A mini review of neuromorphic architectures and implementations," *IEEE Trans. Electron Devices*, vol. 63, no. 10, pp. 3819–3829, Oct. 2016, doi: 10.1109/TED.2016.2598413.

- [7] M. Suri, O. Bichler, D. Querlioz, O. Cueto, L. Perniola, V. Sousa, D. Vuillaume, C. Gamrat, and B. DeSalvo, "Phase change memory as synapse for ultra-dense neuromorphic systems: Application to complex visual pattern extraction," in *IEDM Tech. Dig.*, Dec. 2011, p. 4, doi: 10.1109/IEDM.2011.6131488.

- [8] M. Suri, V. Sousa, L. Perniola, D. Vuillaume, and B. DeSalvo, "Phase change memory for synaptic plasticity application in neuromorphic systems," in *Proc. Int. Joint Conf. Neural Netw.*, Jul. 2011, pp. 619–624, doi: 10.1109/IJCNN.2011.6033278.

- [9] A. Sebastian, M. L. Gallo, G. W. Burr, S. Kim, M. BrightSky, and E. Eleftheriou, "Tutorial: Brain-inspired computing using phase-change memory devices," *J. Appl. Phys.*, vol. 124, no. 11, Sep. 2018, Art. no. 111101, doi: 10.1063/1.5042413.

- [10] N. Gong, T. Idé, S. Kim, I. Boybat, A. Sebastian, V. Narayanan, and T. Ando, "Signal and noise extraction from analog memory elements for neuromorphic computing," *Nature Commun.*, vol. 9, no. 1, pp. 1–8, Dec. 2018, doi: 10.1038/s41467-018-04485-1.

- [11] I. Boybat, M. Le Gallo, S. R. Nandakumar, T. Moraitis, T. Parnell, T. Tuma, B. Rajendran, Y. Leblebici, A. Sebastian, and E. Eleftheriou, "Neuromorphic computing with multi-memristive synapses," *Nature Commun.*, vol. 9, no. 1, pp. 1–12, Dec. 2018, doi: 10.1038/s41467-018-04933-v.

- [12] W. Kim, R. L. Bruce, T. Masuda, G. W. Fraczak, N. Gong, P. Adusumilli, S. Ambrogio, H. Tsai, J. Bruley, J.-P. Han, M. Longstreet, F. Carta, K. Suu, and M. BrightSky, "Confined PCM-based analog synaptic devices offering low resistance-drift and 1000 programmable states for deep learning," in *Symp. VLSI Technol. Dig. Tech. Papers*, Jun. 2019, pp. T66–T67, doi: 10.23919/VLSIT.2019.8776551.

- [13] S. Braga, A. Sanasi, A. Cabrini, and G. Torelli, "Voltage-driven partial-RESET multilevel programming in phase-change memories," *IEEE Trans. Electron Devices*, vol. 57, no. 10, pp. 2556–2563, Oct. 2010, doi: 10.1109/TED.2010.2062185.

- [14] D. Kuzum, R. G. D. Jeyasingh, B. Lee, and H.-S.-P. Wong, "Nanoelectronic programmable synapses based on phase change materials for brain-inspired computing," *Nano Lett.*, vol. 12, no. 5, pp. 2179–2186, May 2012, doi: 10.1021/nl201040y.

- [15] S. La Barbera, D. R. B. Ly, G. Navarro, N. Castellani, O. Cueto, G. Bourgeois, B. D. Salvo, E. Nowak, D. Querlioz, and E. Vianello, "Narrow heater bottom electrode-based phase change memory as a bidirectional artificial synapse," *Adv. Electron. Mater.*, vol. 4, no. 9, Sep. 2018, Art. no. 1800223, doi: 10.1002/aelm.201800223.

- [16] C. M. Neumann, "The effect of interfaces on phase change memory switching," Ph.D. dissertation, Dept. EE, Stanford Univ., Stanford, CA, USA, 2019.

- [17] K. Stern, N. Wainstein, Y. Keller, C. M. Neumann, E. Pop, S. Kvatinsky, and E. Yalon, "Uncovering phase change memory energy limits by sub-nanosecond probing of power dissipation dynamics," *Adv. Electron. Mater.*, Jun. 2021, Art. no. 2100217, doi: 10.1002/aelm.202100217.

- [18] E. Bozorg-Grayeli, J. P. Reifenberg, M. Asheghi, H.-S.-P. Wong, and K. E. Goodson, "Thermal transport in phase change memory materials," *Annu. Rev. Heat Transf.*, vol. 16, no. 1, pp. 397–428, May 2013, doi: 10.1615/annualrevheattransfer.v16.130.

- [19] E. Yalon, S. Deshmukh, M. M. Rojo, F. Lian, C. M. Neumann, F. Xiong, and E. Pop, "Spatially resolved thermometry of resistive memory devices," *Sci. Rep.*, vol. 7, no. 1, pp. 1–8, Dec. 2017, doi: 10.1038/s41598-017-14498-3.

- [20] R. Islam, H. Li, P.-Y. Chen, W. Wan, H.-Y. Chen, B. Gao, H. Wu, S. Yu, K. Saraswat, and H.-S. P. Wong, "Device and materials requirements for neuromorphic computing," *J. Phys. D, Appl. Phys.*, vol. 52, no. 11, Jan. 2019, Art. no. 113001, doi: 10.1088/1361-6463/aaf784.

- [21] W. Zhang, B. Gao, J. Tang, P. Yao, S. Yu, M.-F. Chang, H.-J. Yoo, H. Qian, and H. Wu, "Neuro-inspired computing chips," *Nature Electron.*, vol. 3, no. 7, pp. 371–382, Jul. 2020, doi: 10.1038/s41928-020-0435-7.

- [22] E. Yalon, K. Okabe, C. M. Neumann, H.-S.-P. Wong, and E. Pop, "Energy-efficient phase change memory programming by nanosecond pulses," in *Device Res. Conf. Dig. DRC*, Jun. 2018, pp. 1–2, doi: 10.1109/DRC.2018.8443164.

- [23] N. Papandreou, A. Pantazi, A. Sebastian, E. Eleftheriou, M. Breitwisch, C. Lam, and H. Pozidis, "Estimation of amorphous fraction in multilevel phase-change memory cells," *Solid-State Electron.*, vol. 54, no. 9, pp. 991–996, Sep. 2010, doi: 10.1016/j.sse.2010.04.020.

- [24] S. R. Ovshinsky, "Reversible electrical switching phenomena in disordered structures," *Phys. Rev. Lett.*, vol. 21, no. 20, pp. 1450–1453, Nov. 1968, doi: 10.1103/PhysRevLett.21.1450.

- [25] A. Pirovano, A. L. Lacaita, F. Pellizzer, S. A. Kostylev, A. Benvenuti, and R. Bez, "Low-field amorphous state resistance and threshold voltage drift in chalcogenide materials," *IEEE Trans. Electron Devices*, vol. 51, no. 5, pp. 714–719, May 2004, doi: 10.1109/TED.2004.825805.

- [26] S. Braga, A. Cabrini, and G. Torelli, "Dependence of resistance drift on the amorphous cap size in phase change memory arrays," *Appl. Phys. Lett.*, vol. 94, no. 9, Mar. 2009, Art. no. 092112, doi: 10.1063/1.3088859.

- [27] J. Li, B. Luan, and C. Lam, "Resistance drift in phase change memory," in *Proc. IEEE IRPS*, Apr. 2012, pp. 6C.1.1–6C.1.6, doi: 10.1109/IRPS.2012.6241871.

- [28] N. Papandreou, A. Pantazi, A. Sebastian, M. Breitwisch, C. Lam, H. Pozidis, and E. Eleftheriou, "Multilevel phase-change memory," in Proc. IEEE Int. Conf. Electron., Circuits Syst. (ICECS), Dec. 2010, pp. 1017–1020, doi: 10.1109/ICECS.2010.5724687.