# VO<sub>2</sub> Switch for Electrostatic Discharge Protection

Stephanie M. Bohaichuk<sup>®</sup>, Mario M. Pelella, *Senior Member, IEEE*, Yifei Sun, Zhen Zhang, Shriram Ramanathan, and Eric Pop<sup>®</sup>, *Senior Member, IEEE*

Abstract—On-chip protection from electrostatic discharge (ESD) and electrical overstress (EOS) is a continuous challenge in the semiconductor industry, requiring significant design costs and die space. Insulator-metal transition (IMT) materials like vanadium dioxide (VO<sub>2</sub>) could be used as bidirectional, compact voltage snapback devices for ESD protection that are not required to be in the front-end silicon. However, the reliability and response of these materials to ESD is not yet well studied. Here, we perform transmission line pulse (TLP) tests on thin film (50 - 150 nm) VO<sub>2</sub> devices. These can repeatedly sustain high currents in their metallic state, but still return to insulating once an ESD event is over. Devices with widths from 5 to 50  $\mu$ m can carry a maximum current ( $I_{t2}$ ) from  $\sim$ 1 to over 10 A, equivalent to  $\sim$ 1 to 15 kV of ESD protection. Furthermore, the snapback voltage can be engineered by varying the device length. These results suggest that IMT materials could be promising for use in on-chip ESD/EOS protection.

Index Terms—Electrostatic discharge (ESD), insulator-metal transition (IMT), transmission line pulse (TLP), vanadium dioxide (VO<sub>2</sub>), voltage snapback.

#### I. INTRODUCTION

ROTECTING against electrostatic discharge (ESD) is an ongoing challenge in the manufacturing of electronics, with substantial cost implications [1]. ESD events occur when a build-up of charge is rapidly released into the pins of a chip due to contact with manufacturing/testing tools or human operators. Such events are characterized by large currents of several Amperes on time scales of nanoseconds, which can be extremely destructive to electronics. For example, ESD events can damage ultra-thin transistor gate dielectrics [2] or cause sudden failure of interconnects [3], [4], and are increasingly challenging when reducing these components to smaller dimensions [5]. The more general class of events, where the chip sees a higher voltage or current than it was designed to handle, is referred to as electrical overstress (EOS), and requires similar protection on larger time scales [6].

Manuscript received December 3, 2019; accepted December 16, 2019. Date of publication December 30, 2019; date of current version January 27, 2020. This work was supported by the Stanford SystemX Alliance and Office of Naval Research under Grant N00014-16-1-2398. The review of this letter was arranged by Editor B. Govoreanu. (Corresponding author: Eric Pop.)

Stephanie M. Bohaichuk and Eric Pop are with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: epop@stanford.edu).

Mario M. Pelella is with ON Semiconductor, Santa Clara, CA 95054 USA.

Yifei Sun, Zhen Zhang, and Shriram Ramanathan are with the School of Materials Engineering, Purdue University, West Lafayette, IN 47097 USA. Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2019.2963046

To divert large ESD currents away from sensitive devices, on-chip ESD clamps must become conductive within nanoseconds, then return to insulating once the event has passed. Insulator-metal transition (IMT) materials like vanadium dioxide (VO<sub>2</sub>) inherently have this behavior, with a drop in resistivity by several orders of magnitude once their transition temperature  $T_{\text{IMT}}$  is reached [7]. In two-terminal IMT devices, volatile resistive switching can be triggered at a critical voltage using Joule heating [8], which must be designed larger than the chip operating voltage when used for ESD protection. Using IMT-based voltage snapback devices for ESD protection is promising [9], especially because they are bidirectional, compact, and potentially back-end-of-line (BEOL) compatible, unlike traditional protection. Existing silicon-based solutions take up significant area [10] and moving to compact devices closer to the package pins could lead to significant cost and performance benefits. The required ratings for protection during ESD and leakage current during normal operation depend on a given chip's sensitivity and its environment, but >500 V protection under the human body model (HBM) is typical and >2 kV is ideal [11].

However, an understanding of IMT material behavior at the time scales and currents relevant to ESD is currently lacking. Here we use transmission line pulse (TLP) testing, an industry standard technique that emulates the short time scales and high energies of ESD events [12], to evaluate the snapback and current carrying capability ( $I_{12}$ ) of thin film VO<sub>2</sub> devices. Unlike DC measurements of VO<sub>2</sub> devices, which use a current compliance resistor and limit the accessible on/off ratio [13], TLP measurements do not have a current compliance and fully access the metallic "on" state of the device, in order to determine its failure point. These represent the highest current stress measurements (up to 10 A) of an IMT device to date. We also assess the sensitivity of TLP behavior to device geometry, finding that such IMT-based ESD devices are highly area-efficient compared to silicon-based diodes.

## II. DEVICES

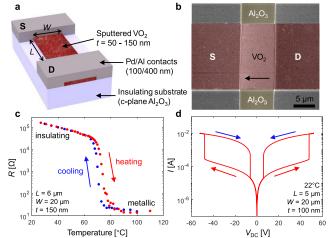

A schematic of the two-terminal VO<sub>2</sub> devices used for TLP testing is shown in Fig. 1(a), and a scanning electron micrograph (SEM) of a typical finished device is shown in Fig. 1(b). VO<sub>2</sub> thin films (with thickness t=50, 100, 150 nm) were grown on c-plane sapphire substrates using physical vapour deposition (PVD) of a V<sub>2</sub>O<sub>5</sub> target with Ar sputtering [14]. The VO<sub>2</sub> was patterned into rectangular stripes using optical lithography and CF<sub>4</sub>/Ar dry etching (60 sccm CF<sub>4</sub>, 30 sccm Ar, 5 mTorr, 500 W ICP power, 100 W bias power,  $\sim$ 50 nm/min etch rate). Contacts were defined by a second optical lithography step and electron-beam evaporation of 100 nm of Pd then 400 nm of Al, followed by

Fig. 1. (a) Diagram of a two-terminal VO $_2$  device used for transmission line pulse (TLP) testing. (b) Top view SEM image of a finished device ( $W=15~\mu\text{m},~L=8~\mu\text{m},~t=100~\text{nm}$ ). Arrow shows direction of current flow. (c) Measured resistance of a device as a function of temperature, with the VO $_2$  showing an insulator-metal transition (IMT) near  $T_{\text{IMT}}\approx70^{\circ}\text{C}$ . (d) Typical voltage-controlled DC characteristics of another VO $_2$  device, showing volatile, bidirectional switching.

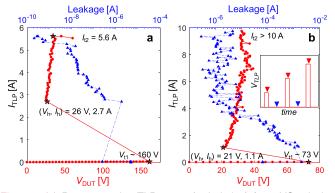

Fig. 2. (a) Representative TLP curve (red circles) for a VO $_2$  device ( $L=10~\mu \rm m$ ,  $W=10~\mu \rm m$ ,  $t=100~\rm nm$ ), showing voltage snapback at  $V_{t1}$  due to IMT. The device eventually fails as open at a maximum current of  $I_{t2}=5.6$  A. Stars label the trigger voltage  $V_{t1}$ , hold voltage  $V_{h}$ , and failure  $I_{t2}$ . DC leakage (blue triangles) is measured at 5 V after each pulse, and decreases with increasing pulses. (b) TLP curve of a VO $_2$  device ( $L=6~\mu \rm m$ ,  $W=50~\mu \rm m$ ,  $t=150~\rm nm$ ) that survived up to  $\sim 10~\rm A$  of current (the instrument limit). The inset schematic shows when  $I_{TLP}$  and  $V_{DUT}$  (red) as well as leakage at 5 V DC (blue) are measured.

lift-off. SPR 220-3 photoresist with 3  $\mu$ m thickness was used because of the poor selectivity of the dry etch, and to aid with lift-off. Devices tested had VO<sub>2</sub> widths of W=5 to 50  $\mu$ m and lengths of L=1 to 15  $\mu$ m, as shown in Fig. 1(a).

The temperature-dependent resistance of a VO<sub>2</sub> device is shown in Fig. 1(c), with the VO<sub>2</sub> displaying IMT near 70°C and a change in resistance by  $>10^3\times$ . Once it cools, the VO<sub>2</sub> returns to insulating, with a temperature hysteresis of  $\sim$ 5°C. Voltage-controlled DC switching is shown in Fig. 1(d). As the voltage increases (red arrow), the VO<sub>2</sub> is Joule-heated to its IMT temperature and it abruptly switches to the metallic state at  $|V_{\rm IMT}|$ . After this point, the power dissipated in the device is much higher due to the lower resistance in the metallic state. Thus, the voltage must decrease much further (blue arrow) for the device to cool and return to its insulating state. In DC measurements a 5 k $\Omega$  resistor is used in series with the device as a current compliance to avoid damage due to overheating in the metallic state, limiting the on/off

resistance ratio. Switching is repeatable and bidirectional, i.e. independent of voltage polarity in all devices measured.

## III. TRANSMISSION LINE PULSE (TLP) TESTING

Fig. 2 displays TLP testing done at room temperature by inputting a series of 100 ns square pulses with 10 ns rise and fall times into the device under test (DUT) with increasing voltage, until the device failed. Voltage ( $V_{\rm DUT}$ ) and current ( $I_{\rm TLP}$ ) in the DUT were measured between 70 to 90 ns on the output TLP waveform. The pulse rate was  $\sim$ 10/min (the device had time to cool between pulses), and DC leakage current was measured at 5 V between pulses, to assess degradation. No current compliance was used.

TLP curves (red) with post-pulse DC leakage (blue) for typical VO<sub>2</sub> devices are shown in Fig. 2, with the inset schematic showing when each measurement is taken. The leakage is plotted along the top axis, as a function of  $I_{TLP}$ (vertical axis). The VO<sub>2</sub> remains in its insulating state until it undergoes an IMT to the metallic state at  $V_{t1}$ , triggering a voltage snapback to  $V_{\rm h} \sim 25~{\rm V}$  (the snapback is due to the device's change in resistance and therefore its impedance mismatch with the transmission line or ESD source). This is accompanied by an increase in current by several orders of magnitude. Once each pulse is over, the VO2 returns to its insulating state due to the volatile nature of its IMT, confirmed by the post-pulse leakage. Stressing the device similar to an ESD event, each pulse with  $V > V_{t1}$  triggers an IMT. Beyond  $I_{t2}$  the device fails as open and is no longer capable of an IMT and voltage snapback. All measured devices show similar TLP characteristics regardless of bias polarity, handling both positive and negative ESD events.

The VO<sub>2</sub> devices can carry a maximum current  $I_{t2}$  ranging from  $\sim$ 1 to over 10 A (the instrument limit), surviving from  $\sim$ 2 ESD-like TLP switching events in smaller devices to >100 in the larger devices tested. (Even surviving a handful of ESD events is sufficient for device qualification.) This is equivalent to ESD protection of  $\sim$ 1 to 15 kV under the human body model [15]. Assuming a uniform current flow, this suggests current densities of  $\sim$ 100 to 950 MA/cm<sup>2</sup> in the VO<sub>2</sub> strip. However, the IMT is likely initiated in a localized "filament" where the VO<sub>2</sub> is hottest [16], meaning the actual current densities and local temperature rises are much higher. For comparison, typical Cu, Al, or CuAl interconnects can carry  $\sim$ 70 to 150 MA/cm<sup>2</sup> when tested under the HBM [4], [17]–[19].

The insulating state leakage of the  $VO_2$  typically starts near several  $\mu A$ , and is smaller in narrow devices. After the first TLP to trigger snapback, leakage can either increase or decrease slightly. As the device is subjected to more TLP, leakage decreases (Fig. 2) due to increasing damage to both the  $VO_2$  and the contacts, until failure as an open.

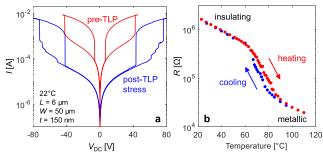

If TLP testing is stopped well before failure, or the  $\sim 10$  A limit is reached without failure [e.g. in Fig. 2(b)], then the VO<sub>2</sub> still shows temperature-induced IMT and DC switching behavior, but with lower performance. Fig. 3(a) shows voltage-controlled DC switching behavior with a 5 k $\Omega$  series resistor for the device in Fig. 2(b) before and after TLP. There is still bidirectional, volatile switching, but the switching voltage has increased (likely due to changes in current flow and self-heating). Fig. 3(b) shows that IMT is still present near 70°C, but it is less sharp and lower in magnitude, indicat-

Fig. 3. (a) DC voltage-controlled switching of the device in Fig. 2(b) before (red) and after (blue) TLP. Despite having carried ~10 A, the device still shows volatile bidirectional switching after TLP. (b) Resistance of the same device as a function of temperature after TLP measurements. There is still an IMT, but with reduced magnitude and abruptness.

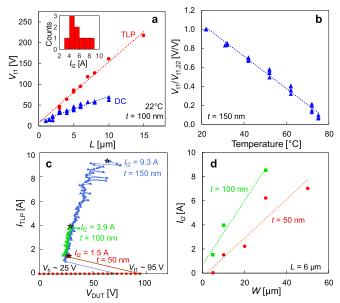

Fig. 4. (a) Room temperature switching voltage  $V_{t1}$  in DC (blue triangles) and TLP (red circles) increases linearly with device length. The inset shows the distribution of  $I_{t2}$  values measured in the TLP devices corresponding to the red circles ( $W=10~\mu\text{m},~t=100~\text{nm}$ ). (b) DC  $V_{t1}$  normalized to  $V_{t1}$  at 22°C reduces with increasing ambient temperature (L=1 to 15  $\mu\text{m}$ ). (c) TLP curves for devices with different thicknesses ( $L=6~\mu\text{m},~W=10~\mu\text{m}$ ).  $V_{t1}$  and  $V_{h}$  are unaffected, but  $I_{t2}$  improves with increased thickness. (d)  $I_{t2}$  from TLP for VO $_{t2}$  devices with different widths and thicknesses. Dashed lines represent linear fits.

ing changes to at least part of the VO<sub>2</sub> channel. Further study is needed to better understand the origin of these changes.

Fig. 4(a) shows that device switching voltage  $V_{t1}$  in both DC and TLP decreases linearly with reducing device length. This occurs because shorter devices have lower resistance, requiring lower voltages to reach the IMT temperature. Linear fits give a slope of 14.6  $\pm$  0.6 V/ $\mu$ m and 6.1  $\pm$  0.3 V/ $\mu$ m for TLP and DC switching, respectively. For all devices, the switching voltage in TLP is roughly double the DC switching voltage. Since the time scales of TLP are much shorter than DC, device heating at a given voltage is much lower. Thus, higher voltages are needed to reach the IMT temperature during TLP. The vertical axis intercept  $\sim 8$  V is primarily associated with contact resistance ( $\sim 200 \text{ k}\Omega \cdot \mu\text{m}$  when insulating) and heat loss at the contacts, and may represent a minimum DC switching voltage [20]. Reducing contact resistance to the VO<sub>2</sub> is expected to reduce this intercept [21], enabling sub-8 V applications.

Length appears to have no impact on  $I_{t2}$  or reliability for the range of devices measured. Thus, length provides a simple way of engineering the ESD clamp's trigger voltage to be above the chip operating voltage. The distribution of  $I_{t2}$  values measured for the TLP devices in Fig. 4a is shown as an inset, with a mean of 5.7 A and standard deviation of 1.4 A.

The DC switching voltage  $V_{t1}$  decreases by 1.7% per 1°C increase in ambient temperature, extracted from a linear fit to Fig. 4(b). This shift is reported as a percentage because its absolute magnitude depends on device length. The  $V_{t1}$  shift is partly due to the reduced temperature rise and therefore power required to reach the IMT. The large temperature coefficient of resistance (TCR) of the VO<sub>2</sub> in its insulating state also contributes to a reduction in  $V_{t1}$ , because of increased self-heating, and to an increase in leakage current with increasing temperature. For ESD protection devices, this means that the DC  $V_{t1}$  must be designed higher than the chip operating voltage with a margin to account for any increases in chip temperature.

Fig. 4(c) shows  $I_{t2}$  improves with increasing VO<sub>2</sub> thickness, with minimal impact on  $V_{t1}$ . Similarly, Fig. 4(d) shows that using wider devices results in higher  $I_{t2}$  and survival of more ESD events, but this comes at the cost of higher leakage current. Linear fits give approximate slopes of  $220 \pm 60 \text{ V}/\mu\text{m}$  and  $400 \pm 60 \text{ V}/\mu\text{m}$  under the HBM model [15] for the 50 nm and 100 nm films, respectively. This is highly areaefficient compared to  $\sim 20$  to  $80 \text{ V}/\mu\text{m}$  for silicon-based diodes [10], [22], [23], and is expected to improve with increasing thickness or potential BEOL integration.

Further study of the failure mechanism in  $VO_2$  devices is needed, which might be due to defect migration (e.g. oxygen vacancy migration [24], changes to the  $VO_2$  stoichiometry [25], or voids) or in part to contact degradation. It is expected that  $I_{t2}$  could be improved by reducing the local temperature in the device. This could be done by adding electrically insulating but thermally conductive heat spreading layers next to the  $VO_2$ , e.g.  $Al_2O_3$ , AlN, or h-BN [26]. However, because the IMT is thermally driven, this would increase  $V_{t1}$ . Finally, we note that although our existing devices survive sufficiently many ESD events to be of practical use, their robustness could be further improved by increasing device dimensions (thickness and width) and improving their contacts.

## IV. CONCLUSION

Materials with an IMT could enable the development of highly compact devices for bidirectional ESD protection, with the potential to be implemented in the back-end for silicon area savings. Here, we have assessed the current carrying capability of VO<sub>2</sub> as a prototypical IMT material for ESD protection, using TLP measurements. VO<sub>2</sub> devices can sustain several Amperes of current and repeatably undergo IMT in response to ESD-like energies. For ESD protection of chips with higher operating temperatures than 70°C or lower leakage requirements, other IMT materials with a higher band gap and transition temperature, and lower TCR in the insulating state, could be explored, such as NbO<sub>2</sub> [27], [28].

### **ACKNOWLEDGMENT**

The authors acknowledge the Sunnyvale Characterization Lab at ON Semiconductor for assistance with TLP measurements.

### REFERENCES

- J. E. Vinson and J. J. Liou, "Electrostatic discharge in semiconductor devices: An overview," *Proc. IEEE*, vol. 86, no. 2, pp. 399–420, Feb. 1998, doi: 10.1109/5.659493.

- [2] A. Ille, W. Stadler, T. Pompl, H. Gossner, T. Brodbeck, K. Esmark, P. Riess, D. Alvarez, K. Chatty, R. Gauthier, and A. Bravaix, "Reliability aspects of gate oxide under ESD pulse stress," in *Proc. Electr. Over*stress/Electrostatic Discharge Symp., Anaheim, CA, USA, Sep. 2007, pp. 6A.1-1-6A.1-10, doi: 10.1109/EOSESD.2007.4401771.

- [3] K. Banerjee, A. Amerasekera, N. Cheung, and C. Hu, "High-current failure model for VLSI interconnects under short-pulse stress conditions," *IEEE Electron Device Lett.*, vol. 18, no. 9, pp. 405–407, Sep. 1997, doi: 10.1109/55.622511.

- [4] S. H. Voldman, "The impact of technology scaling on ESD robustness of aluminum and copper interconnects in advanced semiconductor technologies," *IEEE Trans. Comp., Packag., Manufact. Technol. C*, vol. 21, no. 4, pp. 265–277, Oct. 1998, doi: 10.1109/3476.739176.

- [5] C. Russ, "ESD issues in advanced CMOS bulk and FinFET technologies: Processing, protection devices and circuit strategies," *Microelectron. Rel.*, vol. 48, nos. 8–9, pp. 1403–1411, Aug. 2008, doi: 10.1016/j.microrel.2008.07.042.

- [6] K. T. Kaschani and R. Gärtner, "The impact of electrical overstress on the design, handling, and application of integrated circuits," in *Proc. Electr. Overstress/Electrostatic Discharge Symp.*, Anaheim, CA, USA, Sep. 2011, pp. 1–10.

- [7] Z. Yang, C. Ko, and S. Ramanathan, "Oxide electronics utilizing ultrafast metal-insulator transitions," *Annu. Rev. Mater. Res.*, vol. 41, no. 1, pp. 337–367, Aug. 2011, doi: 10.1146/annurev-matsci-062910-100347.

- [8] D. Li, A. A. Sharma, D. K. Gala, N. Shukla, H. Paik, S. Datta, D. G. Schlom, J. A. Bain, and M. Skowronski, "Joule heating—induced metal—insulator transition in epitaxial VO<sub>2</sub>/TiO<sub>2</sub> devices," ACS Appl. Mater. Inter., vol. 8, no. 20, pp. 12908–12914, May 2016, doi: 10.1021/acsami.6b03501.

- [9] B.-J. Kim, Y. W. Lee, S. Choi, S. J. Yun, and H.-T. Kim, "VO<sub>2</sub> thin film varistor based on metal-insulator transition," *IEEE Electron Device Lett.*, vol. 31, no. 1, pp. 14–16, Jan. 2010, doi: 10.1109/LED.2009.2034763.

- [10] C.-Y. Lin, P.-H. Wu, and M.-D. Ker, "Area–efficient and low–leakage diode string for on–chip ESD protection," *IEEE Trans. Electron Devices*, vol. 63, no. 2, pp. 531–536, Feb. 2016, doi: 10.1109/ted.2015.2504493.

- [11] Recommended ESD Target Level for HBM Qualification, document JEP155B, JEDEC, Jul. 2018.

- [12] S. H. Voldman, R. Ashton, J. Barth, D. Bennett, J. Bernier, M. Chaine, J. Daughton, E. Grund, M. Farris, H. Gieser, L. G. Henry, M. Hopkins, H. Hyatt, M. I. Natarajan, P. Juliano, T. J. Maloney, B. McCaffrey, L. Ting, and E. Worley, "Standardization of the transmission line pulse (TLP) methodology for electrostatic discharge (ESD)," in *Proc. Electr. Overstress/Electrostatic Discharge Symp.*, Las Vegas, NV, USA, Sep. 2003, pp. 1–10.

- [13] L. Sánchez, A. Rosa, A. Griol, A. Gutierrez, P. Homm, B. Van Bilzen, M. Menghini, J. P. Locquet, and P. Sanchis, "Impact of the external resistance on the switching power consumption in VO<sub>2</sub> nano gap junctions," *Appl. Phys. Lett.*, vol. 11, no. 3, Jul. 2017, Art. no. 031904, doi: 10.1063/1.4994326.

- [14] Z. Zhang, F. Zuo, C. Wan, A. Dutta, J. Kim, J. Rensberg, R. Nawrodt, H. H. Park, T. J. Larrabee, X. Guan, Y. Zhou, S. M. Prokes, C. Ronning, V. M. Shalaev, A. Boltasseva, M. A. Kats, and S. Ramanathan, "Evolution of metallicity in vanadium dioxide by creation of oxygen vacancies," *Phys. Rev. Appl.*, vol. 7, no. 3, Mar. 2017, Art. no. 034008, doi: 10.1103/PhysRevApplied.7.034008.

- [15] J. E. Barth, K. Verhaege, L. G. Henry, and J. Richner, "TLP calibration, correlation, standards, and new techniques," *IEEE Trans. Electron. Packag. Manufact.*, vol. 24, no. 2, pp. 99–108, Apr. 2001, doi: 10.1109/6104.930960.

- [16] H. Madan, M. Jerry, A. Pogrebnyakov, T. Mayer, and S. Datta, "Quantitative mapping of phase coexistence in Mott–Peierls insulator during electronic and thermally driven phase transition," ACS Nano, vol. 9, no. 2, pp. 2009–2017, Feb. 2015, doi: 10.1021/nn507048d.

- [17] S. H. Voldman, "Evolution, revolution, and technology scaling—The impact on ESD and EOS reliability," *Front. Mater.*, vol. 5, pp. 1–10, Jul. 2018, doi: 10.3389/fmats.2018.00033.

- [18] K. Banerjee, A. Amerasekera, and C. Hu, "Characterization of VLSI circuit interconnect heating and failure under ESD conditions," in *Proc. Int. Rel. Phys. Symp.*, Dallas, TX, USA, Apr. 1996, pp. 237–245, doi: 10.1109/RELPHY.1996.492126.

- [19] Z. Dong, F. Lu, L. Wang, R. Ma, C. Zhang, H. Zhao, A. Wang, S. Wen, R. Wong, R. Fung, C. Chu, J. Watt, A. Jahanzeb, and P. Liaw, "ESD characterization and design guidelines for interconnects in 28 nm CMOS," in *Proc. IEEE Int. Interconnect Technol. Conf.*, San Jose, CA, USA, May 2014, pp. 99–102, doi: 10.1109/IITC.2014. 6831845.

- [20] S. M. Bohaichuk, M. Muñoz Rojo, G. Pitner, C. J. McClellan, F. Lian, J. Li, J. Jeong, M. G. Samant, S. S. P. Parkin, H.-S. P. Wong, and E. Pop, "Localized triggering of the insulator-metal transition in VO<sub>2</sub> using a single carbon nanotube," ACS Nano, vol. 13, no. 10, pp. 11070–11077, Aug. 2019, doi: 10.1021/acsnano.9b03397.

- [21] A. Joushaghani, J. Jeong, S. Paradis, D. Alain, J. S. Aitchison, and J. K. S. Poon, "Voltage-controlled switching and thermal effects in VO<sub>2</sub> nano-gap junctions," *Appl. Phys. Lett.*, vol. 104, no. 22, Jun. 2014, Art. no. 221904, doi: 10.1063/1.4881155.

- [22] A. Z. H. Wang and C.-H. Tsay, "On a dual-polarity on-chip electrostatic discharge protection structure," *IEEE Trans. Electron Devices*, vol. 48, no. 5, pp. 978–984, May 2001, doi: 10.1109/16. 918246.

- [23] S. H. Voldman and V. P. Gross, "Scaling, optimization and design considerations of electrostatic discharge protection circuits in CMOS technology," *J. Electrostatics*, vol. 33, no. 3, pp. 327–356, Oct. 1994, doi: 10.1016/0304-3886(94)90038-8.

- [24] J. Jeong, N. Aetukuri, T. Graf, T. D. Schladt, M. G. Samant, and S. S. P. Parkin, "Suppression of metal-insulator transition in VO<sub>2</sub> by electric field-induced oxygen vacancy formation," *Science*, vol. 339, no. 6126, pp. 1402–1405, Mar. 2013, doi: 10.1126/science.1230512.

- [25] J. del Valle, Y. Kalcheim, J. Trastoy, A. Charnukha, D. N. Basov, and I. K. Schuller, "Electrically induced multiple metal-insulator transitions in oxide nanodevices," *Phys. Rev. Appl.*, vol. 8, no. 5, Nov. 2017, Art. no. 054041, doi: 10.1103/physrevapplied.8.054041.

- [26] R. L. Xu, M. Muñoz Rojo, S. M. Islam, A. Sood, B. Vareskic, A. Katre, N. Mingo, K. E. Goodson, H. G. Xing, D. Jena, and E. Pop, "Thermal conductivity of crystalline AlN and the influence of atomic-scale defects," *J. Appl. Phys.*, vol. 126, no. 18, Nov. 2019, Art. no. 185105, doi: 10.1063/1.5097172.

- [27] H. R. Philipp and L. M. Levinson, "NbO<sub>2</sub> devices for subnanosecond transient protection," *J. Appl. Phys.*, vol. 50, no. 7, pp. 4814–4822, Jul. 1979, doi: 10.1063/1.326544.

- [28] T. Joshi, T. R. Senty, P. Borisov, A. D. Bristow, and D. Lederman, "Preparation, characterization, and electrical properties of epitaxial NbO<sub>2</sub> thin film lateral devices," *J. Phys. D, Appl. Phys.*, vol. 48, no. 33, Jul. 2015, Art. no. 335308, doi: 10.1088/0022-3727/48/33/ 335308.